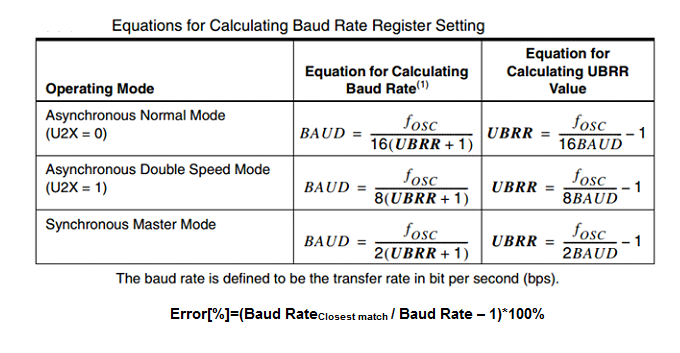

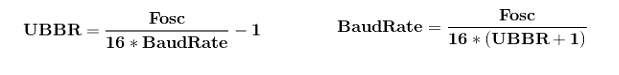

Speed (Baud rate)

USART Pin Configuration

AVR basic Registers

UDR: USART Data Register

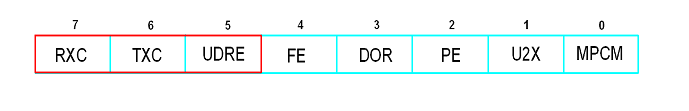

UCSRA

UBRR

UCSRA: USART Control and Status Register A

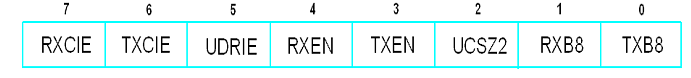

UCSRB: USART Control and Status Register B

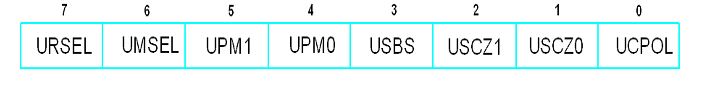

UCSRC: USART Control and Status Register C

UBRRL and UBRRH: USART Baud Rate Registers

/* Name : UARTmain.c

* Purpose : Source code for UART interface with ATMEGA16.

* Author : Gemicates

* Date : 2017-09-09

* Website : www.gemicates.org

* Revision : None

*/

#ifndef F_CPU

#define F_CPU 8000000UL // 8 MHz clock speed

#endif

#include<avr/io.h>

volatile char Rec_Data;

int main()

{

DDRD = 0X02; // PORTD 2nd pin Is set as Output (RD1=1)

UCSRA = 0X00; // Clears TXC & RXC Flag Bit

UCSRB = 0X18; // Transmission Enabling (TXEN=1)

UCSRC = 0X86; // URSEL=1,UMSEL=0,UCSZ1=1,UCSZ0=0

UBRRL = 51; // Serial Baudrate=9600

UDR = 'B'; // Transmit a charcter

while((UCSRA & 0X20)!=0X20); // UDRE Flag Bit Check

while(1)

{

while((UCSRA & 0X80)!=0X80); // RXE Bit Check

Rec_Data=UDR; // Double Buffered TX/RX Register

UDR= Rec_Data;

while((UCSRA & 0X20)!=0X20); // UDRE Flag Bit Check

}

}